## Datasheet

### Disea

NK !H\$, \$E M< !\$%

ÖÒË€Í Ë€FH

The information contained in this document has been carefully researched and is, to the best of our knowledge, accurate. However, we assume no liability for any product failures or damages, immediate or consequential, resulting from the use of the information provided herein. Our products are not intended for use in systems in which failures of product could result in personal injury. All trademarks mentioned herein are property of their respective owners. All specifications are subject to change without notice.

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | DISEA<br>Stomized Display           | Electro    | onics Co., LTD       |

|---------------------------------------|-------------------------------------|------------|----------------------|

|                                       | PRODUCT SPE                         |            | ATIONS               |

| For Cu                                | stomer:                             | □ : APPROV | AL FOR SPECIFICATION |

| Custor                                | mer Model No                        | □ : APPROV | AL FOR SAMPLE        |

| Modu<br><b>ble of Cont</b>            | le No.: <u>ZW-T080QYH-01</u>        | Date :_    | 2016-07-01           |

| No.                                   | Item                                |            | Page                 |

| 1                                     | Cover Sheet(Table of Contents)      |            |                      |

| 2                                     | Revision Record                     |            |                      |

| 3                                     | General Specifications              |            |                      |

| 4                                     | Outline Drawing                     |            |                      |

| 5                                     | Absolute Maximum Ratings            |            |                      |

| 6                                     | Electrical Specifications           |            |                      |

| 7                                     | Optical Characteristics             |            |                      |

| 8                                     | Reliability Test Items and Criteria |            |                      |

| 9                                     | Precautions for Use of LCD Modules  |            |                      |

|                                       |                                     |            |                      |

| r Custom                              | er's Acceptance:                    | 0          |                      |

# Approved By Comment

| PREPARED | CHECKED | VERIFIED BY QA DEPT | VERIFIED BY R&D DEPT |

|----------|---------|---------------------|----------------------|

| mma      | john    |                     | Dmjiang              |

### 2. Revision Record

| Date       | Rev.No | Page | Revision Items    | Prepared |

|------------|--------|------|-------------------|----------|

| 2016-07-01 | V0     |      | The first release | ZHP      |

| 2017-09-26 | V1     |      | Update drawing    | Stone    |

| 2018-08-01 | V2     |      | Update the format | mma      |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

|            |        |      |                   |          |

#### 3. General Specifications

*ZW*-T080QYH-01 is a TFT-LCD module. It is composed of a TFT-LCD panel, driver IC, FPC, a back light unit. The 8.0" display area contains 800 x1280 pixels and can display up to 16.7M colors. This product accords with RoHS environmental criterion.

| Item                  | Contents                        | Unit    | Note |

|-----------------------|---------------------------------|---------|------|

| LCD Type              | TFT/Transmissive/Normally White | -       |      |

| Display color         | 16.7M                           |         |      |

| Viewing Direction     | Full viewing angle              | O'Clock |      |

| Operating temperature | -10~+50                         | °C      |      |

| Storage temperature   | -20~+60                         | °C      |      |

| Module size           | 114.7x184.2x2.55                | mm      |      |

| Active Area(W×H)      | 107.64X172.22                   | mm      |      |

| Number of Dots        | 800×1280                        | dots    |      |

| TFT Controller        | N/A                             | -       |      |

| Power Supply Voltage  | 1.8                             | V       |      |

| Backlight             | 21LEDs (white)                  | pcs     |      |

| Weight                |                                 | g       |      |

| Interface             | 4Lanes-MIPI                     | -       |      |

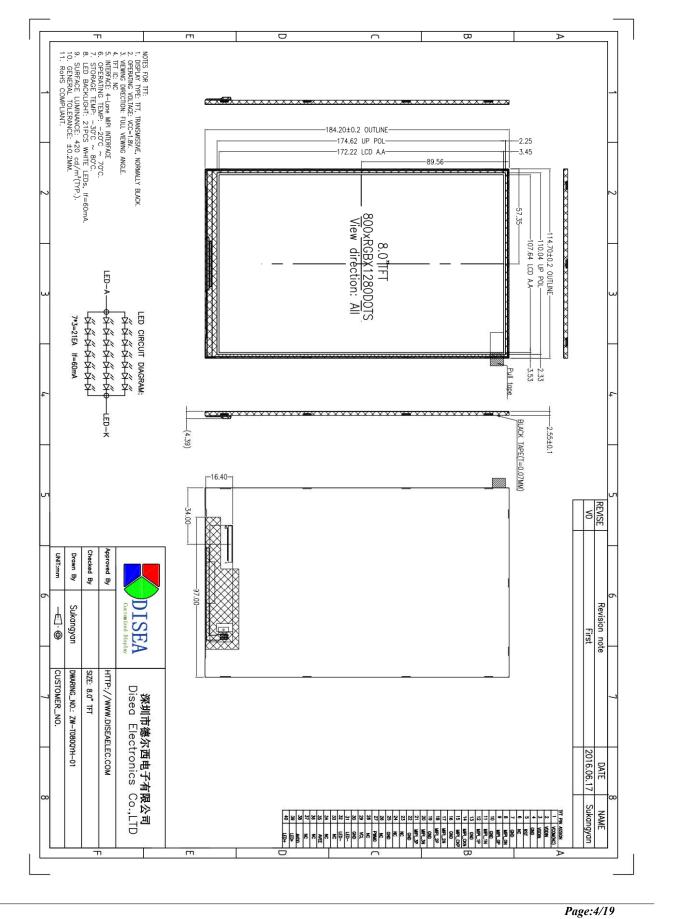

#### 4. Outline. Drawing

#### 5. Absolute Maximum Ratings(Ta=25 °C)

#### 5.1 Electrical Absolute Maximum Ratings.(Vss=0V , Ta=25 $^{\circ}C$ )

| Item                 | Symbol | Min. | Max. | Unit | Note |

|----------------------|--------|------|------|------|------|

| Power Supply Voltage | VDDIN  | -0.3 | 5.5  | V    |      |

|                      | AVDD   | -0.3 | 6.6  |      | 1, 2 |

|                      | AVEE   | +0.3 | -6.6 | V    |      |

Notes:

1. If the module is above these absolute maximum ratings. It may become permanently damaged. Using the module within the following electrical characteristic conditions are also exceeded, the module will malfunction and cause poor reliability.

#### 5.2 Environmental Absolute Maximum Ratings.

| Item                | Stor          | age         | Operat | ting        | Note |

|---------------------|---------------|-------------|--------|-------------|------|

| nem                 | MIN.          | MAX.        | MIN.   | MAX.        | NOLE |

| Ambient Temperature | <b>-20</b> °C | <b>60</b> ℃ | -10°C  | <b>50</b> ℃ | 1,2  |

| Humidity            | -             | -           | -      | -           | 3    |

- 1. The response time will become lower when operated at low temperature.

- 2. Background color changes slightly depending on ambient temperature.

The phenomenon is reversible.

3. Ta<=40 °С:85%RH MAX.

Ta>=40 C:Absolute humidity must be lower than the humidity of 85%RH at 40 C.

#### 6. Electrical Specifications and Instruction Code

#### 6.1 Electrical characteristics(Vss=0V ,Ta=25 °C)

| Parameter |       | Symbol           | Condition       | Min                | Тур  | Max                | Unit | Note |

|-----------|-------|------------------|-----------------|--------------------|------|--------------------|------|------|

|           |       | VDDIN            | <b>Ta=25°</b> ℃ | 1.7                | 1.8  | 1.9                | V    |      |

| Power su  | pply  | AVDD             | <b>Ta=25</b> ℃  | 5.2                | 5.8  | 6.0                | V    |      |

|           |       | AVEE             | <b>Ta=25°</b> ℃ | -6.0               | -5.8 | -5.2               | V    |      |

| Input     | 'H'   | VIH              | -               | 0.7V <sub>CC</sub> | -    | Vcc                | V    |      |

| voltage   | 'L'   | V <sub>IL</sub>  | -               | 0                  | -    | 0.3V <sub>CC</sub> | V    |      |

| Current   |       | I <sub>CC1</sub> | Normal<br>mode  | -                  | -    | -                  | mA   |      |

| Consump   | otion | I <sub>CC2</sub> | Sleep<br>mode   | -                  | -    | -                  | mA   |      |

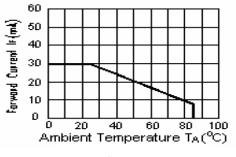

#### 6.2 LED backlight specification(VSS=0V ,Ta=25°C)

| Item           | Symbol         | Condition | Min | Тур | Max   | Unit | Note |

|----------------|----------------|-----------|-----|-----|-------|------|------|

| Supply voltage | V <sub>f</sub> | lf=60mA   | 19  | 21  | 23    | V    |      |

| Uniformity     | ∆Вр            | lf=60mA   | 75  | -   | -     | %    |      |

| LED life time  | -              | lf=60mA   | 20k | 30k | Hours |      |      |

Note:

#### 1: VLED=VLED(+)-VLED(-).

2:The current of LED is 20mA.

A LED drive in constant current mode is recommended.

ILED VS TEMP

#### 6.3 Interface signals

| Pin No. | Symbol    | I/O | Function                                                                                        |

|---------|-----------|-----|-------------------------------------------------------------------------------------------------|

| 1       | VCOM      | Р   | Common Voltage(-1.756 ± 0.3 V)                                                                  |

| 2-3     | VDDIN     | Р   | A power supply for the analog power.                                                            |

| 4       | GND       | Р   | Ground.                                                                                         |

| 5       | RST       | I   | Reset pin. Setting either pin low initializes the LSI.<br>Must be reset after power is supplied |

| 6       | NC        | -   | No connection                                                                                   |

| 7       | GND       | Р   | Ground.                                                                                         |

| 8       | MIPI-0N   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 9       | MIPI-0P   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 10      | GND       | Р   | Ground.                                                                                         |

| 11      | MIPI-1N   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 12      | MIPI-1P   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 13      | GND       | Р   | Ground.                                                                                         |

| 14      | MIPI-CLKN | I   | MIPI-DSI CLOCK differential signal input pins.                                                  |

| 15      | MIPI-CLKP | I   | MIPI-DSI CLOCK differential signal input pins.                                                  |

| 16      | GND       | Р   | Ground.                                                                                         |

| 17      | MIPI-2N   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 18      | MIPI-2P   | 1   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 19      | GND       | Р   | Ground.                                                                                         |

| 20      | MIPI-3N   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 21      | MIPI-3P   | I   | MIPI-DSI Data differential signal input pins. (Data                                             |

| 22      | GND       | Р   | Ground.                                                                                         |

| 23-24   | NC        | _   | No connection                                                                                   |

| 25      | GND       | Р   | Ground.                                                                                         |

| 26      | NC        | -   | No connection                                                                                   |

| 27      | PWM0      | I   | CABC PWM signal output.                                                                         |

| 28      | NC        | _   | No connection                                                                                   |

| 29      | VCL       | Р   | Output voltage pin,use it to generate common voltage by a VR circuit (output voltage -2.5V)     |

| 30      | GND       | Р   | Ground.                                                                                         |

| 31-32   | LED-      | Р   | LED back light(Cathode)                                                                         |

| 35      | AVEE      | Р   | Analog supply negative voltage                                                                  |

| 36-37   | NC        | -   | No connection                                                                                   |

| 38      | AVDD      | Р   | Analog supply positive voltage                                                                  |

| 39-40   | LED+      | Р   | LED back light(Anode)                                                                           |

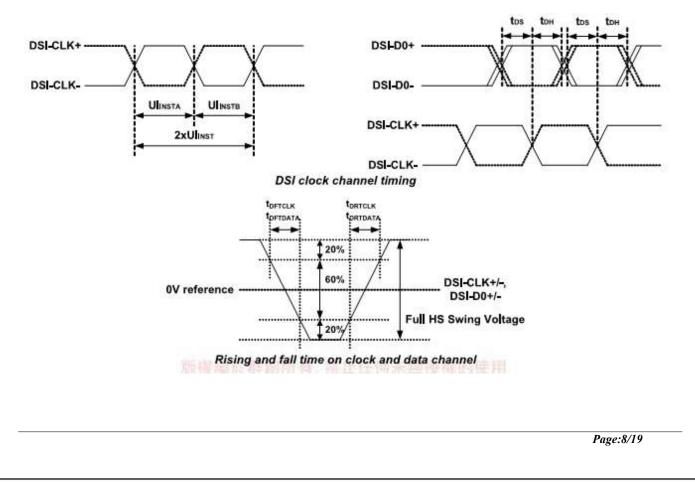

#### 6.4 MIPI signal Timing Characteristics

#### 6.4.1 High Speed Mode

| Signal     | Symbol   | Parameter                           | MIN         | TYP | MAX    | Unit | Description     |

|------------|----------|-------------------------------------|-------------|-----|--------|------|-----------------|

|            |          |                                     | 4           | -   | 8      | ns   | 4 Lane (Note 2) |

| DSI-CLK+/- | 2xUINST  | Double UI instantaneous             | 3           | -   | 8      | ns   | 3 Lane (Note 2) |

|            |          |                                     | 2.352       | -   | 8      | ns   | 2 Lane (Note 3) |

|            | UIINSTA  | Ul instantaneous halfs              | 2           | -   | 4      | ns   | 4 Lane (Note 2) |

| DSI-CLK+/- | UIINSTR  | (UI = UIINSTA =                     | 1.5         | -   | 4      | ns   | 3 Lane (Note 2) |

|            | OINOID   | UIINSTB)                            | 1.176       | -   | 4      | ns   | 2 Lane (Note 3) |

| DSI-Dn+/-  | tDS      | Data to clock setup time            | 0.15x<br>Ul | -   | -      | ps   |                 |

| DSI-Dn+/-  | tDH      | Data to clock hold time             | 0.15x<br>UI | -   | -      | ps   |                 |

| DSI-CLK+/- | tDRTCLK  | Differential rise time for<br>clock | 150         | -   | 0.3xUI | ps   |                 |

| DSI-Dn+/-  | tDRTDATA | Differential rise time for<br>data  | 150         | -   | 0.3xUI | ps   |                 |

| DSI-CLK+/- | tDFTCLK  | Differential fall time for<br>clock | 150         | -   | 0.3xUI | ps   |                 |

| DSI-Dn+/-  | tDFTDATA | Differential fall time for<br>data  | 150         | -   | 0.3xUI | ps   |                 |

Note 1) Dn = D0, D1, D2 and D3.

- Note 2) Maximum total bit rate is 2Gbps for 24-bit data format, 1.5Gbps for 18-bit data format and 1.33Gbps for 16-bit data format in 3 lanes or 4 lanes application which support to 800RGBx 1280 resolution.

- Note 3) Maximum total bit rate is 1.7Gbps for 24-bit data format, 1.275Gbps for 18-bit data format and 1.13Gbps for 16-bit data format in 2 lanes application which support to 720RGBx1280 resolution.

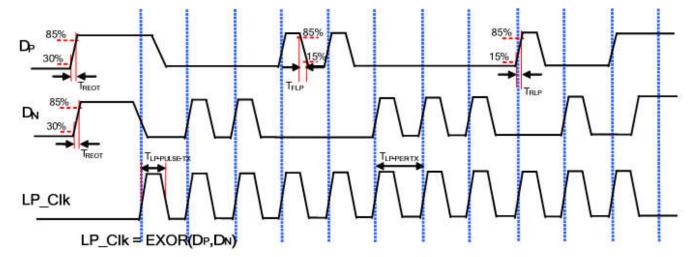

#### 6.4.2 LP Transmission

| Devenueter                                  | Values                              |                   |      | es Unit |      | Domork |

|---------------------------------------------|-------------------------------------|-------------------|------|---------|------|--------|

| Parameter                                   | Symbol                              | Min.              | Тур. | Max.    | Unit | Remark |

| DSI CLK frequency(LP)                       | FDSICLK_LP                          | 8:                |      | 10      | MHz  |        |

| DSI CLK Cycle Time(LP)                      | t <sub>CLKC_LP</sub>                | 100               |      | 41 14   | ns   |        |

| DSI Data Transfer Rate(LP)                  | t <sub>DSIR_LP</sub>                |                   |      | 10      | Mbps |        |

| 15%-85% rise time and fall time             | T <sub>RLP</sub> / T <sub>FLP</sub> | 85 <del>4</del> 5 |      | 35      | ns   |        |

| 30%-85% rise time(from HS to LP)            | T <sub>REOT</sub>                   | -                 | 1    | 35      | ns   |        |

| Pulse width of the LP<br>exclusive-OR clock | t <sub>LP-PULSE-TX</sub>            | 50                | 65   | 1990    | ns   |        |

| Period of the LP exclusive-OR<br>clock      | t <sub>LP-PRE-TX</sub>              | 100               | 130  | 1.75    | ns   |        |

#### 6.4.3 Low Power Mode

| Signal        | Symbol        | Parameter                                                                    | MIN         | TYP | MAX         | Unit | Description |

|---------------|---------------|------------------------------------------------------------------------------|-------------|-----|-------------|------|-------------|

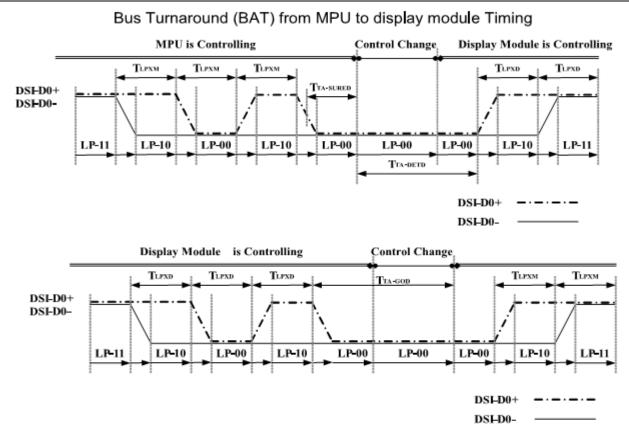

| DSI-D0+<br>/- | TLPXM         | Length of LP-00,<br>LP-01, LP-10 or<br>LP-11 periods<br>MPU ( Display Module | 50          | -   | 75          | ns   | Input       |

| DSI-D0+<br>/- | TLPXD         | Length of LP-00,<br>LP-01, LP-10 or<br>LP-11 periods<br>Display Module ( MPU | 50          | -   | 75          | ns   | Output      |

| DSI-D0+<br>/- | TTA-SU<br>RED | Time-out before the<br>MPU start driving                                     | TLPX<br>D   | 125 | 2xTL<br>PXD | ns   | Output      |

| DSI-D0+<br>/- | TTA-GE<br>TD  | Time to drive LP-00<br>by display module                                     | 5xTL<br>PXD |     | <u>~</u>    | ns   | Input       |

| DSI-D0+<br>/- | TTA-GO<br>D   | Time to drive LP-00<br>after turnaround<br>request - MPU                     | 4xTL<br>PXD |     | -           | ns   | Output      |

Bus Turnaround (BAT) from display module to MPU Timing

#### 6.4.4 DSI Bursts

| Signal                                                   | Symbol                                                                        | Parameter                                                                                                        | MIN      | ТҮР | МАХ     | Unit  | Descripti<br>on |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------|-----|---------|-------|-----------------|--|

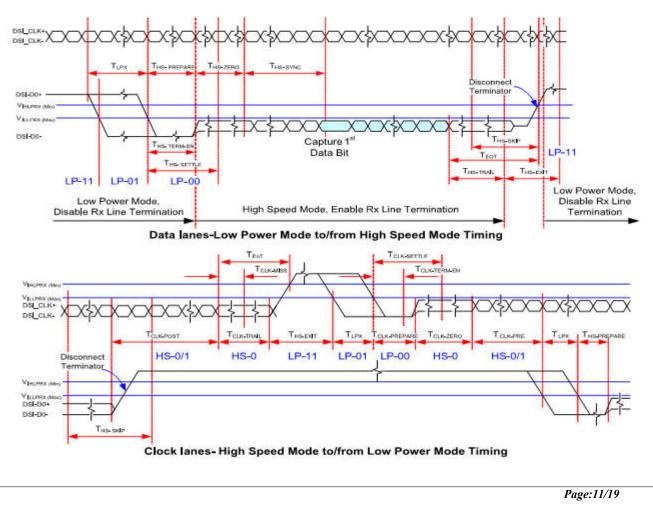

|                                                          | Low Power Mode to High Speed Mode Timing                                      |                                                                                                                  |          |     |         |       |                 |  |

| DSI-Dn+/-                                                | I-Dn+/- TLPX Length of any low power state period                             |                                                                                                                  | 50       | -   | -       | ns    | Input           |  |

| DSI-Dn+/-                                                | SI-Dn+/- THS-PRE PARE PARE Time to drive LP-00 to prepare for HS transmission |                                                                                                                  | 40+4xUl  | -   | 85+6xUI | ns    | Input           |  |

| DSI-Dn+/-                                                |                                                                               | receiver line termination<br>measured from when Dn                                                               | -        | -   | 35+4xUl | ns    | Input           |  |

|                                                          | High Speed Mode to Low Power Mode Timing                                      |                                                                                                                  |          |     |         |       |                 |  |

| DSI-Dn+/-                                                | THS-SKIP                                                                      | Time-out at display module<br>to ignore transition period<br>of EoT                                              | 40       | -   | 55+4xU  | ns    | Input           |  |

| DSI-Dn+/- THS-EXIT Time to drive LP-11 after<br>HS burst |                                                                               | 100                                                                                                              | -        | -   | ns      | Input |                 |  |

| DSI-Dn+/-<br>L<br>THS-TRAI<br>L<br>THS-TRAI<br>DSI-Dn+/- |                                                                               | 60+4xUl                                                                                                          | -        | -   | ns      | Input |                 |  |

| High Speed Mode to/from Low Power Mode Timing            |                                                                               |                                                                                                                  |          |     |         |       |                 |  |

| DSI-CLK+/- TCLK-PO continue sending after the last asso  |                                                                               | Time that the MPU shall<br>continue sending HS clock<br>after the last associated<br>data lane has transition to | 60+52xUI | -   | -       | ns    | Input           |  |

|            |                                                                                           | LP mode                                                                                                                          |              |   |    |    | -     |

|------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|---|----|----|-------|

| DSI-CLK+/- | Time to drive HS                                                                          |                                                                                                                                  | 60           | _ | -  | ns | Input |

| DSI-CLK+/- | THS-EXIT                                                                                  | Time to drive LP-11 after<br>HS burst                                                                                            | 100          | - | -  | ns | Input |

| DSI-CLK+/- | LK+/- TCLK-PR<br>EPARE Time to drive LP-00 to<br>prepare for HS<br>transmission           |                                                                                                                                  | 38           | - | 95 | ns | Input |

| DSI-CLK+/- | TCLK-TE<br>RM-EN<br>Time-out at clock lane<br>display module to enable<br>HS transmission |                                                                                                                                  | -            | - | 38 | ns | Input |

| DSI-CLK+/- | TCLK-PR<br>EPARE+<br>TCLK-ZE<br>RO                                                        | Minimum lead HS-0 drive<br>period before starting clock                                                                          | 300          | - | -  | ns | Input |

| DSI-CLK+/- | TCLK-PR<br>E                                                                              | Time that the HS clock<br>shall be driven prior to any<br>associated data lane<br>beginning the transition<br>from LP to HS mode | 8xU <b>I</b> | - | -  | ns | Input |

Note 1) Dn = D0, D1, D2 and D3.

Note 2) Two HS transmission can be sent with a break as short as THS-EXIT from each other in continuous clock mode. In discontinuous mode, the break is longer which account TCLK-POS, TCLK-TRAIL and THS-EXIT, before activity in clock and data lanes again.

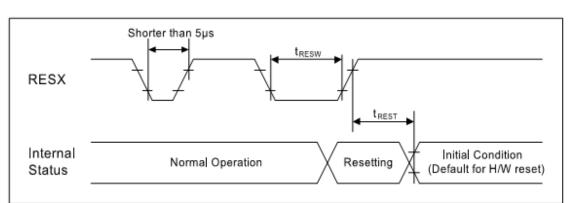

#### 6.4.5 Reset Input Timing

Reset input timing

| (VDDI=1.7~1.9V, VCI=3.0 to 3.6V, GND=0V,Ta = -30 t |                  |                                   |     |     |     | Ta = -30 to 70°C |                                                                 |

|----------------------------------------------------|------------------|-----------------------------------|-----|-----|-----|------------------|-----------------------------------------------------------------|

| Signal                                             | Symbol           | Parameter                         | MIN | ТҮР | MAX | Unit             | Description                                                     |

|                                                    | tresw            | Reset "L" pulse width (Note<br>1) | 10  | -   | -   | μs               |                                                                 |

| RESX                                               | trest Rese<br>2) |                                   | -   | -   | 5   | ms               | When reset<br>applied during<br>Sleep In Mode                   |

|                                                    |                  | Reset complete time (Note 2)      | _   | -   | 120 | ms               | When reset<br>applied during<br>Sleep Out<br>Mode<br>and Note 5 |

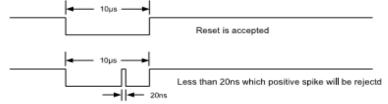

Note 1) Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below.

| RESX Pulse           | Action         |

|----------------------|----------------|

| Shorter than 5µs     | Reset Rejected |

| Longer than 10µs     | Reset          |

| Between 5µs and 10µs | Reset Start    |

- Note 2) During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out –mode. The display remains the blank state in Sleep In–mode) and then return to Default condition for H/W reset.

- Note 3) During Reset Complete Time, values in OTP memory will be latched to internal register during this period. This loading is done every time when there is H/W reset complete time (t<sub>REST</sub>) within 5ms after a rising edge of RESX.

- Note 4) Spike Rejection also applies during a valid reset pulse as shown below:

Page:12/19

#### 7. Optical Characteristics

| Item              | Symbol                           |      | Condition            | Min.  | Тур. | Max.  | Unit              | Note |

|-------------------|----------------------------------|------|----------------------|-------|------|-------|-------------------|------|

| Brightness        | Вр                               |      | <i>θ</i> =0°         | 350   | 420  | -     | Cd/m <sup>2</sup> | 1    |

| Uniformity        | ⊿Вр                              |      | Ф <b>=0</b> °        | 75    | -    | -     | %                 | 1,2  |

|                   | 3:00                             |      | Cr≥10                | 70    | 80   | -     | Deg               | 3    |

| Viewing           | 6:00                             |      |                      | 70    | 80   | -     |                   |      |

| Angle             | 9:00                             |      |                      | 70    | 80   | -     |                   |      |

|                   | 1:                               | 2:00 |                      | 70    | 80   | -     |                   |      |

| Contrast<br>Ratio | Cr                               |      | <i>θ</i> =0°         | 600   | 800  | -     | -                 | 4    |

| Response          | T <sub>r</sub><br>T <sub>f</sub> |      | Φ=0°                 | -     | 25   |       | ms<br>ms          | 5    |

| Time              |                                  |      |                      | -     | 25   |       |                   |      |

|                   | W                                | x    |                      | -0.05 | 0.31 | +0.05 | -                 | -    |

|                   |                                  | У    |                      |       | 0.33 |       | -                 |      |

|                   | R                                | x    | <i>θ</i> =0°<br>Φ=0° |       | -    |       | -                 |      |

| Color of<br>CIE   | R                                | У    |                      |       | -    |       | -                 |      |

| Coordinate        | G<br>B                           | x    |                      |       | -    |       | -                 | 1,6  |

|                   |                                  | у    |                      |       | -    |       | -                 |      |

|                   |                                  | х    |                      |       | -    |       | -                 |      |

|                   | D                                | У    |                      |       | -    |       | -                 |      |

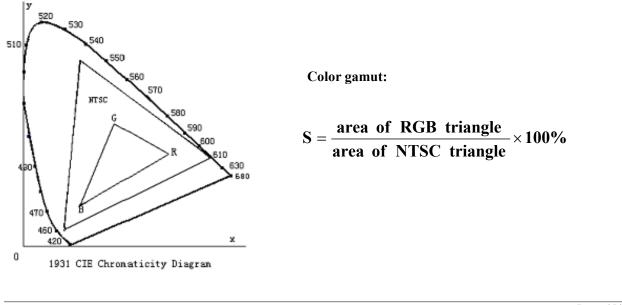

| NTSC<br>Ratio     | S                                |      |                      | 50    | 60   | -     | %                 |      |

Note: The parameter is slightly changed by temperature, driving voltage and materiel

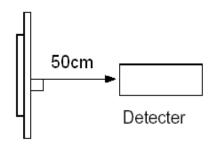

Note 1: The data are measured after LEDs are turned on for 5 minutes. LCM displays full white. The brightness is the average value of 9 measured spots. Measurement equipment BM-7 (Φ5mm) Measuring condition:

- Measuring surroundings: Dark room.

- Measuring temperature: Ta=25 C.

- Adjust operating voltage to get optimum contrast at the center of the display.

Measured value at the center point of LCD panel after more than 5 minutes while backlight turning on.

*Note 2: The luminance uniformity is calculated by using following formula.*

∠Bp = Bp (Min.) / Bp (Max.)×100 (%)

Bp (Max.) = Maximum brightness in 9 measured spots

*Bp* (*Min.*) = *Minimum brightness in 9 measured spots.*

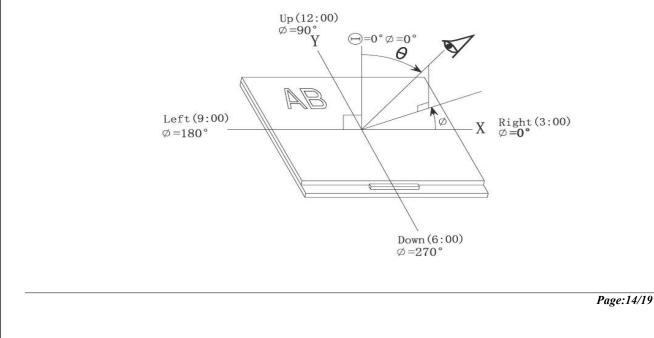

#### Note 3: The definition of viewing angle: Refer to the graph below marked by $\vartheta$ and $\Phi$

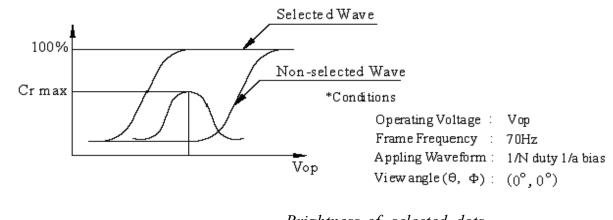

*Note 4: Definition of contrast ratio.( Test LCD using DMS501)*

Contrast ratio(Cr) =  $\frac{Brightness of selected dots}{Brightness of non-selected dots}$

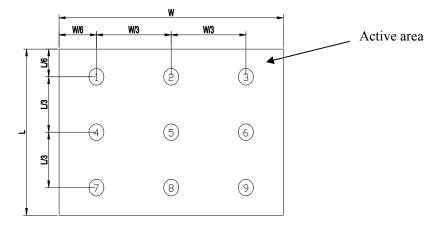

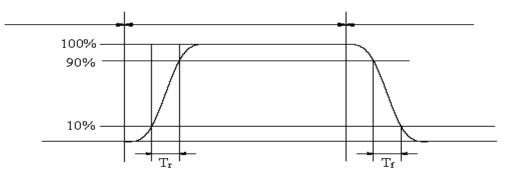

Note 5: Definition of Response time. (Test LCD using DMS501):

The output signals of photo detector are measured when the input signals are changed from "black" to "white" (falling time) and from "white" to "black" (rising time), respectively. The response time is defined as the time interval between the 10% and 90% of amplitudes.Refer to figure as below.

The definition of response time

*Note 6: Definition of Color of CIE Coordinate and NTSC Ratio.*

Page:15/19

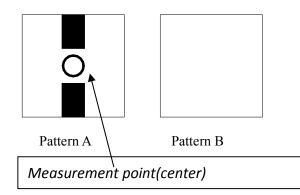

#### Note 7: Definition of cross talk.

Cross talk ratio(%)=|pattern A Brightness-pattern B Brightness|/pattern A Brightness\*100

Electric volume value=3F+/-3Hex

#### 8. Reliability Test Items and Criteria

| No | Test Item                           | Test condition                                                                    | Criterion                                                                   |  |  |

|----|-------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| 1  | High Temperature Storage            | 60℃±2℃ 96H<br>Restore 2H at 25℃<br>Power off                                      |                                                                             |  |  |

| 2  | Low Temperature Storage             | -20℃±2℃ 96H<br>Restore 2H at 25℃<br>Power off                                     |                                                                             |  |  |

| 3  | High Temperature Operation          | 50℃±2℃ 96H<br>Restore 2H at 25℃<br>Power on                                       | 1. After testing,<br>cosmetic and electrical<br>defects should not          |  |  |

| 4  | Low Temperature Operation           | -10℃±2℃ 96H<br>Restore 4H at 25℃<br>Power on                                      | happen.<br>2. Total current<br>consumption should<br>not be more than twice |  |  |

| 5  | High Temperature/Humidity Operation | 40℃±2℃ 90%RH 96H<br>Power on                                                      | of initial value.                                                           |  |  |

| 6  | Temperature Cycle                   | -20°C →60°C<br>30min 5min 30min<br>after 5 cycle, Restore 2H at 25°C<br>Power off |                                                                             |  |  |

| 7  | Vibration Test                      | 10Hz~150Hz, 100m/s², 120min                                                       | Not allowed cosmetic                                                        |  |  |

| 8  | Shock Test                          | Half- sine wave,300m/s <sup>2</sup> ,11ms                                         | and electrical defects.                                                     |  |  |

#### Note: Operation: Supply 1.8V for logic system.

The inspection terms after reliability test, as below

| ITEM       | Inspection        |

|------------|-------------------|

| Contrast   | CR>50%            |

| IDD        | IDD<200%          |

| Brightness | Brightness>60%    |

| Color Tone | Color Tone+/-0,05 |

#### 9. Precautions for Use of LCD Modules

#### 9.1 Handling Precautions

- 9.1.1 The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- 9.1.2 If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- 9.1.3 Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- 9.1.4 The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- 9.1.5 If the display surface is contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

— Isopropyl alcohol — Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water Ketone Aromatic solvents

- 9.1.6 Do not attempt to disassemble the LCD Module.

- 9.1.7 If the logic circuit power is off, do not apply the input signals.

- 9.1.8 To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- a. Be sure to ground the body when handling the LCD Modules.

- b. Tools required for assembly, such as soldering irons, must be properly ground.

- *c.* To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- *d.* The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

#### 9.2 Storage precautions

- 9.2.1 When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

- 9.2.2 The LCD modules should be stored under the storage temperature range. If the LCD modules will be stored for a long time, the recommend condition is:

Temperature : 0  $^\circ\!\!C$   $\sim$  40  $^\circ\!\!C$

Relatively humidity: ≤80%

9.2.3 The LCD modules should be stored in the room without acid, alkali and harmful gas.

# **9.3** The LCD modules should be no falling and violent shocking during transportation, and also should avoid excessive press, water, damp and sunshine.

<u>END</u>

Our company network supports you worldwide with offices in Germany, Austria, Switzerland, the UK and the USA. For more information please contact:

**Headquarters**

FORTEC Elektronik AG Augsburger Str. 2b 82110 Germering

Phone: E-Mail: Internet:

+49 89 894450-0 info@fortecag.de www.fortecad.de

**Fortec Group Members**

Germany

Distec GmbH Office Vienna Nuschinggasse 12 1230 Wien

Phone: E-Mail: Internet: +43 1 8673492-0 info@distec.de www.distec.de

Distec GmbH Augsburger Str. 2b 82110 Germering

Phone: E-Mail: Internet:

+49 89 894363-0 info@distec.de www.distec.de

ALTRAC AG

Bahnhofstraße 3 5436 Würenlos

Phone: E-Mail: Internet:

+41 44 7446111 info@altrac.ch www.altrac.ch

Display Technology Ltd.

Osprey House, 1 Osprey Court Hichingbrooke Business Park Huntingdon, Cambridgeshire, PE29 6FN

Phone: E-Mail: Internet:

+44 1480 411600 info@displaytechnology.co.uk www. displaytechnology.co.uk

Apollo Display Technologies, Corp. 87 Ravnor Avenue. Unit 1Ronkonkoma, NY 11779

Phone: E-Mail: Internet:

+1 631 5804360 info@apollodisplays.com www.apollodisplays.com